その他の機能 | 第5回 - PCI Expressについて 入門編

........

- 更新日

- 2023.05.09

- 公開日

- 2022.04.19

前回、デバイス間でフローコントロールを行うことで、受信バッファの空き不足を要因とするデータロスをなくし、データ転送失敗時のリカバリ機能によりデータ転送が成功する確率が高くなることを説明しました。第6回では、より信頼性を高めるための各種エラーへの対応と、利便性の高い省電力モードについて説明します。

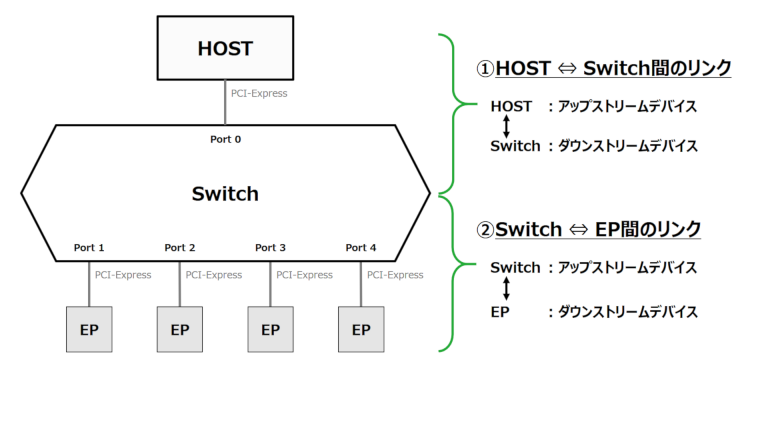

1. アップストリームデバイスとダウンストリームデバイス

PCI Expressは、①HOST-Switch、②Switch-EP(End Point)というリンクで構成されます。各リンクを構成する2つのデバイスのうち、相対的に

ホストデバイスに近いデバイスを「アップストリームデバイス(上流デバイス)」

ホストデバイスから遠いデバイスを「ダウンストリームデバイス(下流デバイス)」

と呼びます。

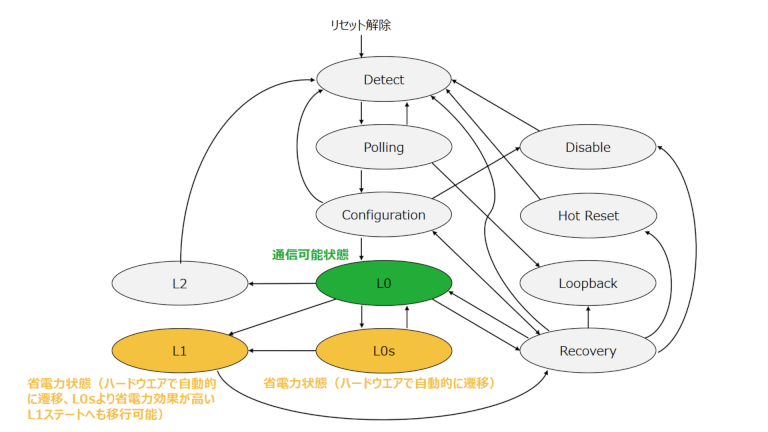

2. 省電力モード

PCI Expressで接続されているデバイスは、 Active State Power Management(ASPM)機能をサポートしています。これはソフトウエアの介在なしで、自動的に、それぞれの送受信部を省電力モードに移行(L0ステート→L0sステート、L0ステート→L1ステート)させることが出来る機能です。L0s・L1ステートへの遷移をリクエスト出来るデバイスは、以下のように限定されています。

L0sステートへの遷移: アップストリームデバイス・ダウンストリームデバイス、共に可

L1ステートへの遷移 : ダウンストリームデバイスのみ可

第3回の記事でLTSSMの各ステートについて述べましたが(第3回 3-2. LTSSM 参照)、ここでも再度、L0, L0s及びL1ステートについて詳しく説明します。

表5-1. L0 / L0s / L1ステート

| ステート | 説明 |

|---|---|

| L0ステート |

|

| L0sステート |

|

| L1ステート |

|

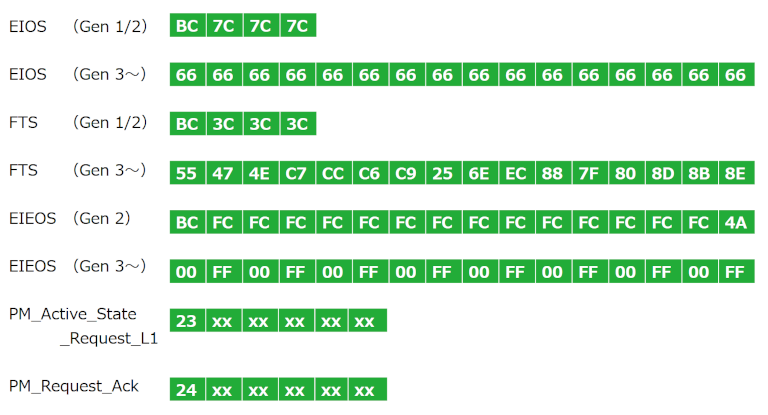

L0ステート→L0sステートへ移行→L0ステートへ復帰の際は、以下のOrdered Setと呼ばれる、3種類の物理レイヤのパケットを使用します。

表5-2. L0-L0s動作で使用されるパケット

| パケット名 | 用途 |

|---|---|

| EIOS(Electrical Idle Ordered Set) | 送信部のL0sステート移行時に、対向デバイスの受信部をL0sステートに移行させるために使用 |

| FTS(Fast Training Sequence Ordered Set) | 送信部のL0ステート移行時に、対向デバイスの受信部をL0ステートに移行させるために使用 |

| EIEOS(Electrical Idle Exit Ordered Set) | 送信部のL0ステート移行時に、対向デバイスの受信部をL0ステートに移行させるために使用、Gen 3(8Gbps)以上のスピードでFTSと組み合わせて使用される |

L0ステート→L1ステートへ移行の際は、以下のDLLP(Data Link Layer Packet)と呼ばれる、 2種類のデータリンクレイヤのパケットを使用します。

表5-3. L0-L1動作で使用されるパケット

| パケット名 | 用途 |

|---|---|

| PM_Active_State_Request_L1 | ダウンストリームデバイスが、アップストリームデバイスに対して、L1ステートに入ることをリクエストするために使用 |

| PM_Request_Ack | アップストリームデバイスが、ダウンストリームデバイスに対して、L1ステートへのリクエストを受け入れたことを通知するために使用 |

それぞれのパケットフォーマットは以下の通りです。

3. L0-L0s間・L0-L1間の遷移動作

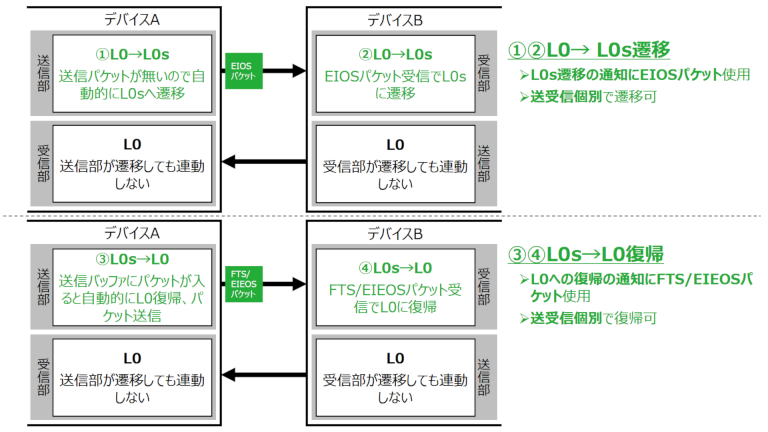

「L0ステート→L0sステートへ遷移→L0ステートへ復帰」のプロセスを、アニメーションで説明します。

アニメーションの動作を、1つの図にまとめました。

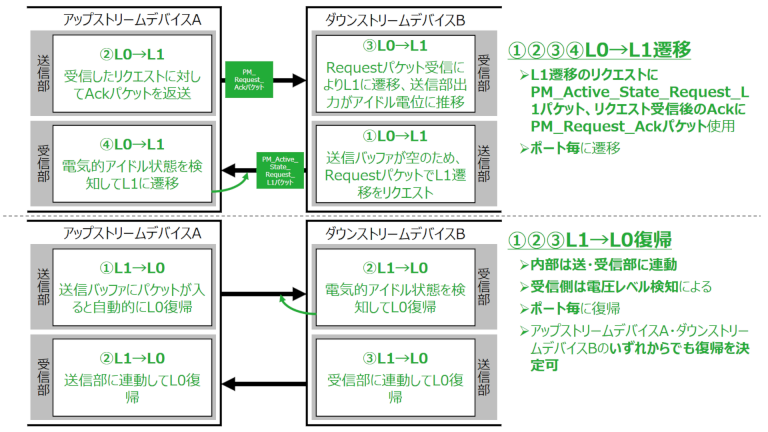

「L0ステート→L1ステートへ遷移→L0ステートへ復帰」のプロセスを、アニメーションで説明します。

アニメーションの動作を、1つの図にまとめました。

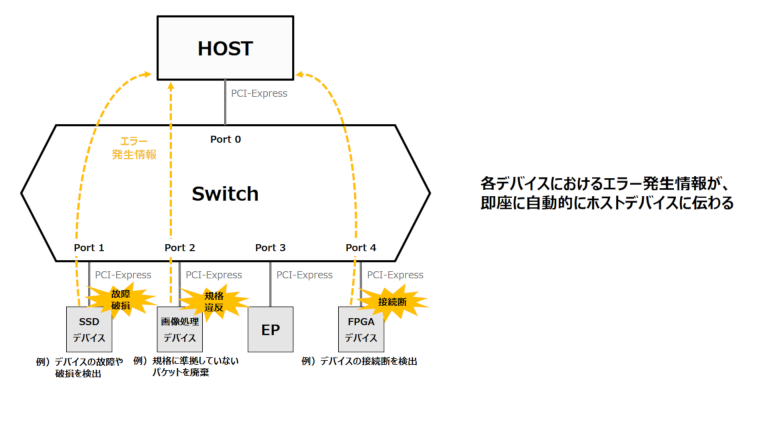

4. エラー通知機能

PCI Expressは、Advanced Error Reporting(AER)機能と呼ばれるエラー通知の仕組みを持っており、発生したエラーに関する情報がホストデバイスへ自動通知されます。なおエラーの項目と重要度は、規格で決められています。

5. エラー分類

規格で規定されているエラーは、CorrectableとUncorrectableの2種類に大別され、Uncorrectable Errorは更にNon FatalとFatalに分類されます。

【1】Correctable Error:ハードウェアにて対処が可能なエラー

【2】Uncorrectable Error:ハードウェアにて対処が不可能なエラー

-

- Non Fatal Error(致命的ではないエラー):パケットは破棄され、ソフトウェアでエラーがリカバリされる

- Fatal Error(致命的なエラー):パケットは破棄され、ソフトウェアでリセットされる

Gen3で既定されているエラー分類の一覧を以下にまとめました。正確な情報は規格書(PCI Express Base Specification Revision 3.0)をご参照ください。

表5-4. 【1】Correctable Error

| エラー名 | エラー内容 | レイヤ |

|---|---|---|

| Receive Error | 受信エラー(8b/10bシンボルエラー、ランニングディスパリティエラー、フレーミングエラー) | PHY |

| Bad TLP | TLP(Transaction Layer Packet)のLCRC(Link CRC)エラー、シーケンスナンバーエラー | DLL |

| Bad DLLP | DLLP(Data Link Layer Packet)のCRCエラー | DLL |

| Replay Timeout | TLP送信後、規定時間内にACK・NAKのいずれも受信できず(パケットの再送信を実施) | DLL |

| Replay NUM Rollover | NAKを4回連続で受信、Replay Timeoutが4回連続で発生 | DLL |

| Header Log Overflow | ヘッダログバッファのオーバーフロー | - |

| Advisory Non-Fatal Error | Non Fatal Errorに属するエラーを検知したが、Non Fatal Errorではないと判断された場合に置き換えられるエラー | - |

| Corrected Internal Error | デバイス内部のエラー(ECCで訂正可能なメモリエラーなどの、動作に影響を与えないエラー) | PMUX |

表5-5. 【2】Uncorrectable Error – 1. Non Fatal Error

| エラー名 | エラー内容 | レイヤ |

|---|---|---|

| Unsupported Request | サポートされていないタイプのリクエストパケットを受信 | TRL |

| アドレスマップに割り当てられていないアドレス空間へのアクセス | ||

| アクセス不可の(Disableされている、存在しない)デバイスやファンクションへのアクセス | ||

| D0ステート以外(D1, D2, D3)でのTLP受信 | ||

| ECRC Error | TLPのECRC(End to End CRC)エラー | |

| Unexpected Completion | 想定外のTD(Transaction ID)を持つコンプリーションパケットを受信 | |

| Completer Abort | プログラミングモデル(アクセス境界、長さなど)の違反 | |

| Completion Timeout | NP(Non Posted Request)タイプのトランザクションでリクエストを発行後、コンプリーションパケットを受信せずに規定時間を超過 | |

| Poisoned TLP | EPフィールド が”1”にセットされたTLPを受信 | |

| ACS Violation | メモリリクエストのAT(Address Translation)の値がデフォルト値でない | |

| MC Blocked TLP | ポートで受信不可に設定されているMC(Multicast)Groupに属するTLPを受信 | |

| AtomicOp Egress Blocked | Disable設定されたポートでAtomicOp(Atomic Operation)を実施 | |

| TLP Prefix Blocked Error | End-End TLP Prefix Blocking Bitが”1”にセットされたポートから、End-End TLP Prefix を含んだTLPを送信 |

表5-6. 【2】Uncorrectable Error – 2. Fatal Error

| エラー名 | エラー内容 | レイヤ |

|---|---|---|

| Malformed TLP | ペイロードサイズとLengthフィールドの設定値が不一致 | TRL |

| ペイロードサイズが最大値を超えている | ||

| TC(Traffic Class)違反(メッセージトランザクションでTC0以外のクラスを使用) | ||

| TCにリンクされていないバーチャルチャネル(VC)を使用 | ||

| コンフィグレーショントランザクション以外で、コンプリーションパケットのCRS(Completion Retry Status)が設定されている | ||

| アドレスバウンダリ規定違反(4KByte境界を跨いだメモリトランザクション) | ||

| Byte Enable規定違反(Byte Enable Bitが正しくセットされていない) | ||

| ダイジェスト規定違反(TDビットが示すダイジェストフィールド有無との不一致) | ||

| RCB(Read Completion Boundary)規定違反(64Byte又は128Byteのアドレス境界をまたがって複数のコンプリーションパケットを発行) | ||

| Receiver Overflow | 受信バッファのオーバーフロー | DLL |

| Flow Control Protocol Error | Update FCパケットのCredit値が正しくない | DLL |

| 未使用Credit発行を規定以上に実施 | ||

| Data Link Protocol Error | シーケンス番号の異常検出(ACKパケットのシーケンス番号が正しくない) | DLL |

| Surprise Down Error | 予期せぬリンクダウン発生(一方のデバイスが電源OFFなど) | - |

| Uncorrectable Internal Error | デバイス内部のエラー(ECCでは訂正できないメモリエラーなど、動作に影響を与えるエラー) | PMUX |

6. まとめ

第5回の今回は、PCI Expressのその他の機能について説明致しました。

PCI Expressは、規格でサポートされている様々な省電力モードやエラー通知機能によって、利便性と信頼性が高められています。これらのおかげで、次回紹介する様々なアプリケーションでの利用が広がっています。

次はいよいよフィナーレを飾る最終回、PCI Expressを搭載したアプリケーションについて説明します。