信頼性の高い接続 | 第3回 - PCI Expressについて 入門編

........

- 更新日

- 2023.05.09

- 公開日

- 2021.12.14

第3回はPCI Expressの特徴の1つである、信頼性の高い接続について説明をしますが、まずは前回のおさらいから。

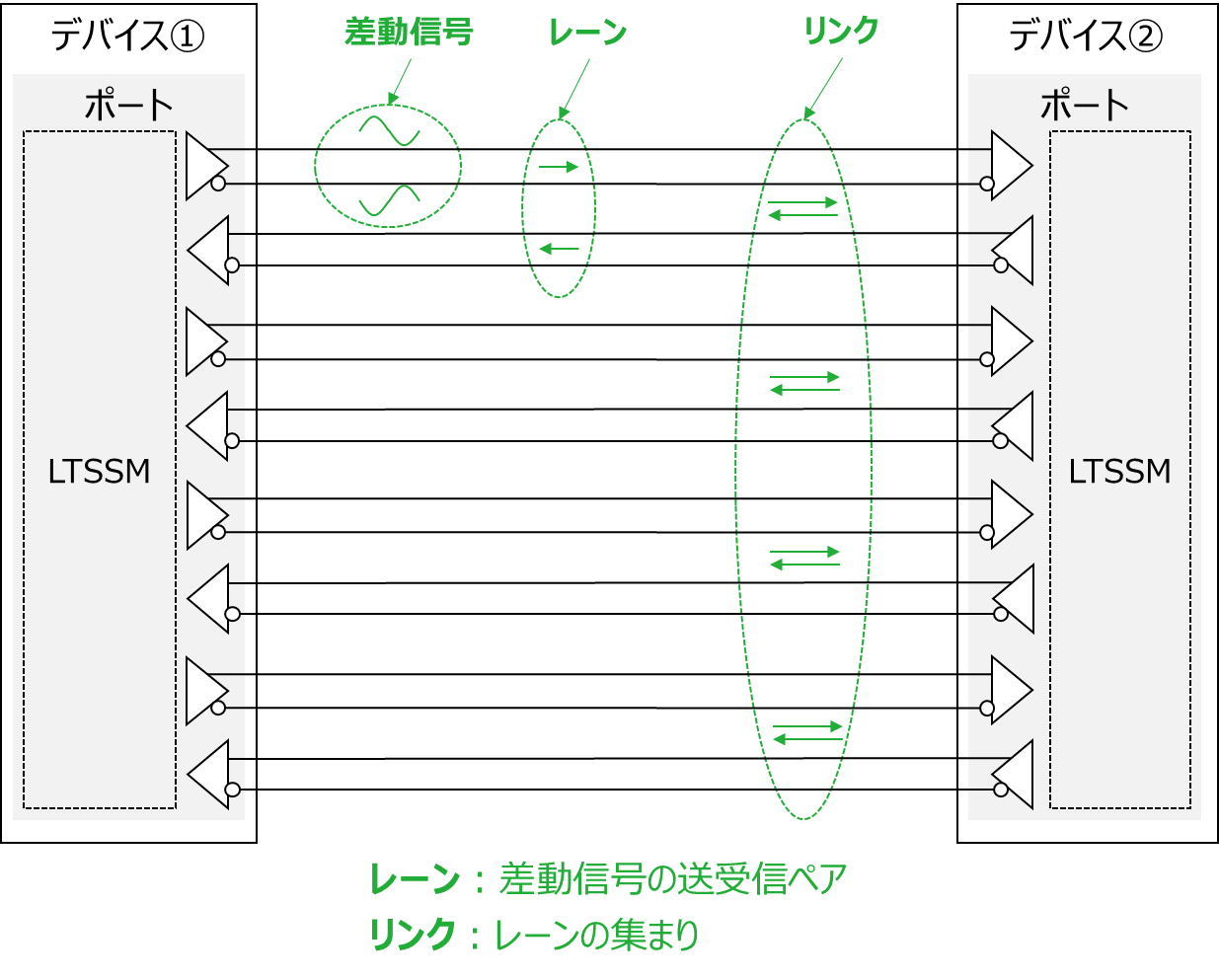

PCI Expressのデバイス間接続では、差動信号の送受信ペアを「レーン」、レーンの集まりを「リンク」と呼びます(図3-1参照)。このリンク状態を管理するため、PCI Expressでは「LTSSM(Link Training and Status State Machine)」と呼ばれる状態遷移機構(ステートマシン)を使用します。PCI Expressの高信頼性接続を理解するには、このLTSSMについて知っておく必要がありますので、次のセクション以降で説明します

1. LTSSM(Link Training and Status State Machine)

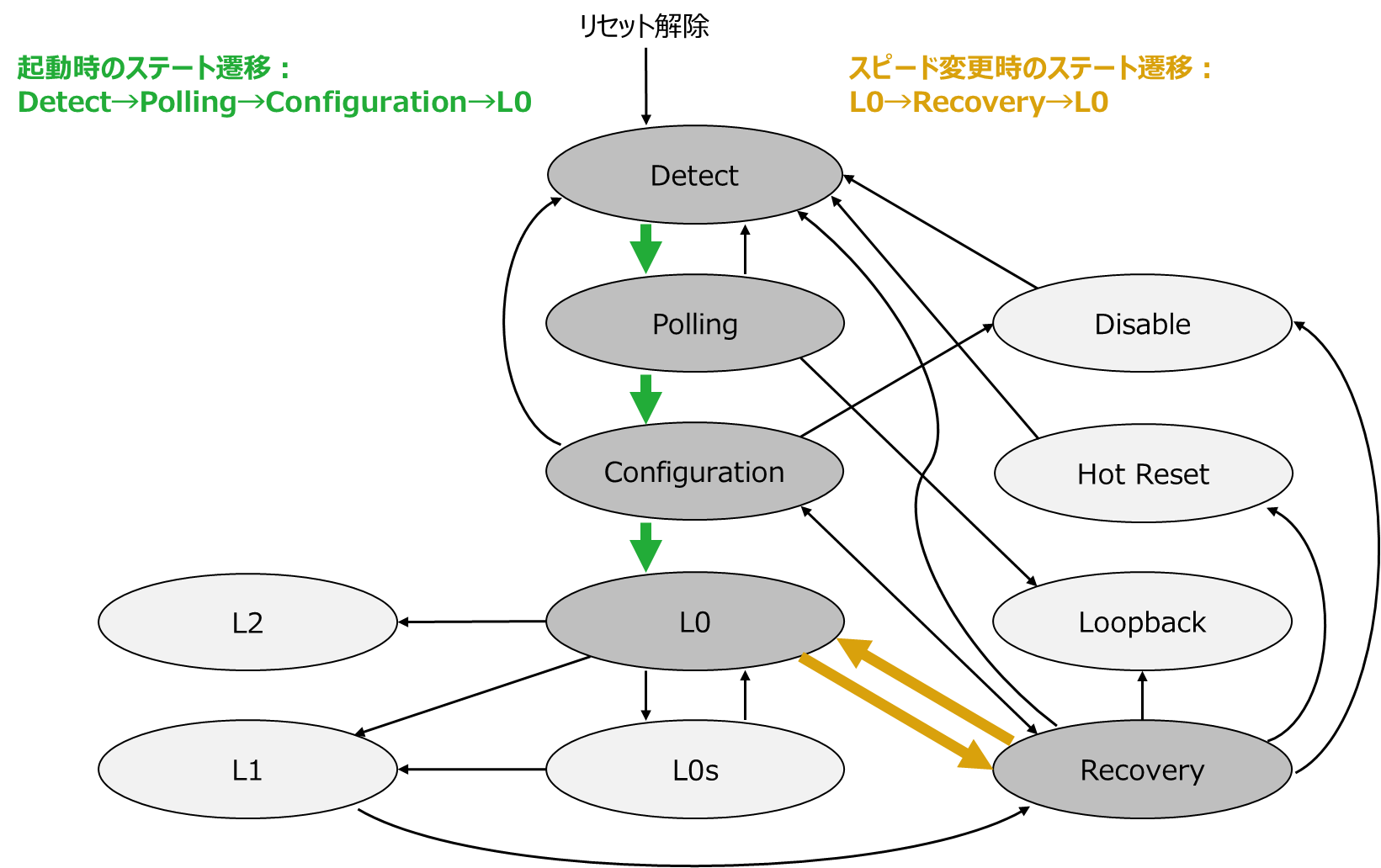

PCI Expressデバイスは、接続されたデバイス間のリンク状態を管理するため、LTSSM(Link Training and Status State Machine)という状態遷移機構(ステートマシン)を備えております。PCI Expressデバイスが起動してステートマシンのリセットが解除された後に、接続されたデバイスそれぞれのステート(状態)が同期・同調して下記のように遷移します。

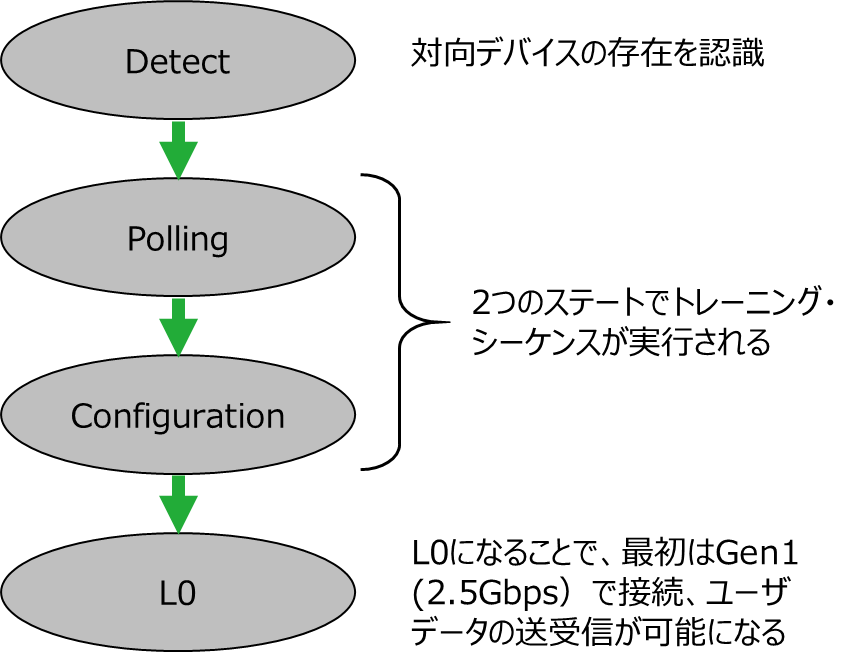

起動時のステート遷移:Detect→Polling→Configuration→L0

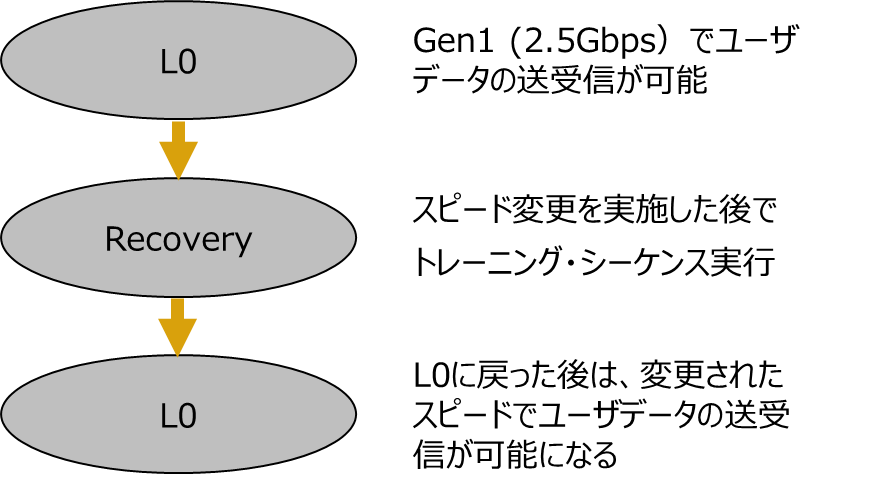

それぞれ共にL0ステートに至った時点で、Gen1(2.5Gbps)のスピードでユーザデータの送受信を開始します。デバイスがGen1以上、例えばGen3(8Gbps)をサポートしている場合は、

スピード変更時のステート遷移:L0→Recovery→L0

と進んでGen3(8Gbps)へスピードアップされ、高速なユーザデータの送受信が出来るようになります。

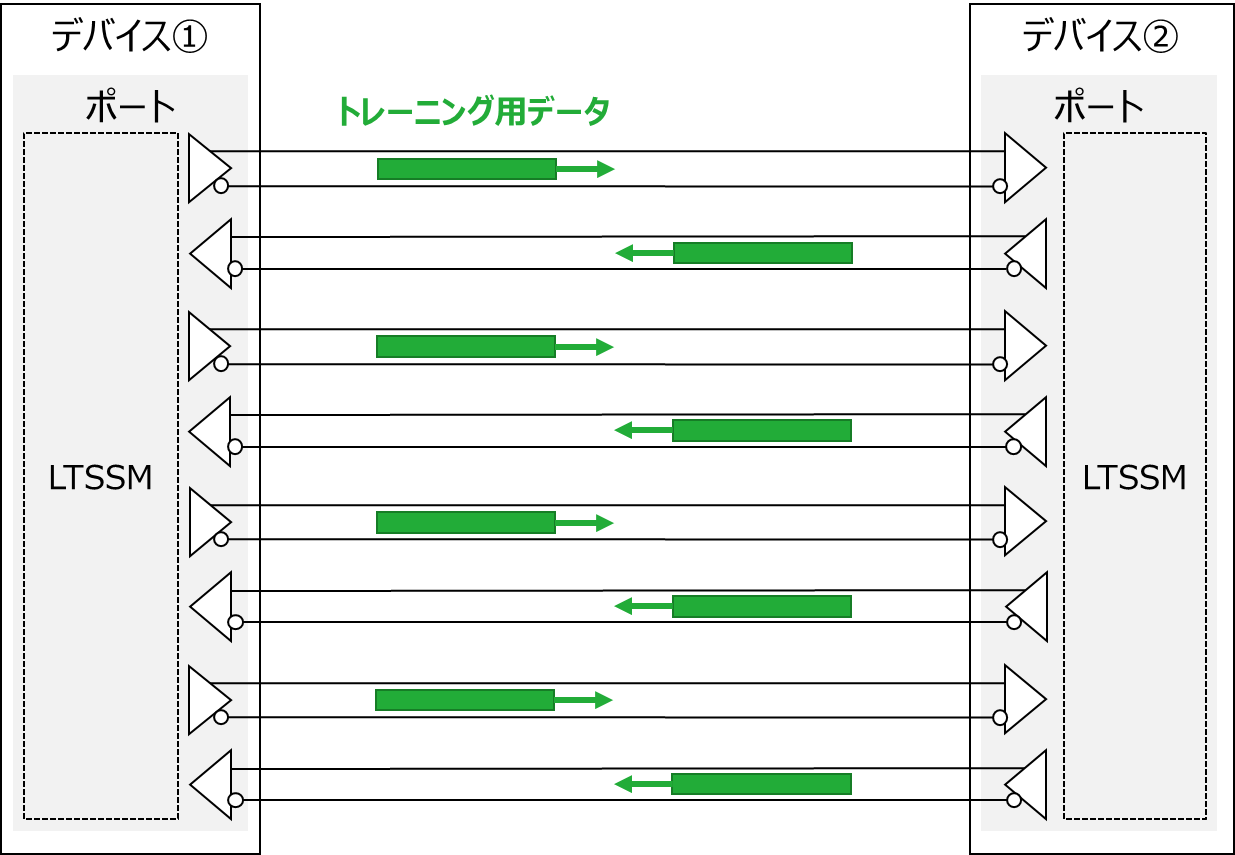

L0ステートで安定した通信状態を確立するため、 L0ステートに入る前にデバイス間でトレーニング・シーケンスを実施します。トレーニング・シーケンスでは各レーンごとにトレーニング用データの送受信が行われ、送受信部に対して様々な調整が自動的に行われます。

LTSSM(Link Training and Status State Machine)の各ステートに関する解説を、以下にまとめました。

表3-1. LTSSM(Link Training and Status State Machine)ステート

| ステート | 解説 |

|---|---|

| Detect | 対向デバイスが存在するか否かを調べる |

| Polling | トレーニング・シーケンス実行、レーン極性調整、ビット同期、シンボル同期を実施 |

| Configuration | トレーニング・シーケンス実行、レーン構成確立、レーン間デスキュー(de-skew)を実施 |

| L0 | 通信可能状態(ユーザデータ送受信可能) |

| Recovery |

以下のいずれかを実施 ①通信不安定状態を解消(ビットエラー多発の場合)

②通信スピード変更(Gen1➞Gen2など)

|

| L0s | 省電力状態(Recovery Stateを経由しないため、短時間でL0ステートに復帰可能) |

| L1 | 省電力状態(L0sステートより低消費電力なステート。Recovery Stateを経由してL0ステートに復帰) |

| L2 | 省電力状態(L1ステートよりさらに低消費電力なステート。送受信ブロックは完全に停止) |

| Disable | リンク使用不可 |

| Loopback | 試験・デバッグ用 |

| Host Reset | Hot Resetが掛かっている状態 |

2. 信頼性の高い接続

PCI Expressデバイス間のトレーニング・シーケンスが実行されることで、送受信部が自動的に調整され、通信可能状態(L0ステート)で安定したユーザデータの送受信が出来るようになります。この動作は、主に以下の3つのケースで行われます。

1) デバイス起動後に対向デバイスを認識した場合

(Detect→Polling→Configurationとステートを遷移しながらトレーニング・シーケンスを実行し、L0へ遷移)

2) L0ステートでスピード変更を要求された場合

(L0→Recoveryにステート遷移してスピードを変更、その後トレーニング・シーケンスを実行、L0に戻る)

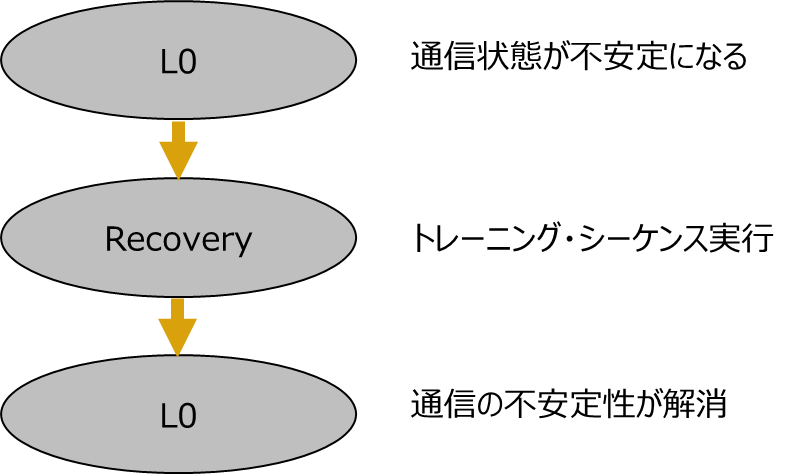

3) L0ステートで通信状態が不安定になり、ビットエラーが多発した場合

(L0→Recoveryにステート遷移してトレーニング・シーケンスを実行、通信状態を安定させてからL0に戻る)

特に上記3) のように、出来る限り通信可能状態を維持する仕組みが設けられておりますので、PCI Expressのデバイス間の接続は、信頼性が高いと言えます。

3. トレーニング・シーケンスに関する用語集

ビット同期

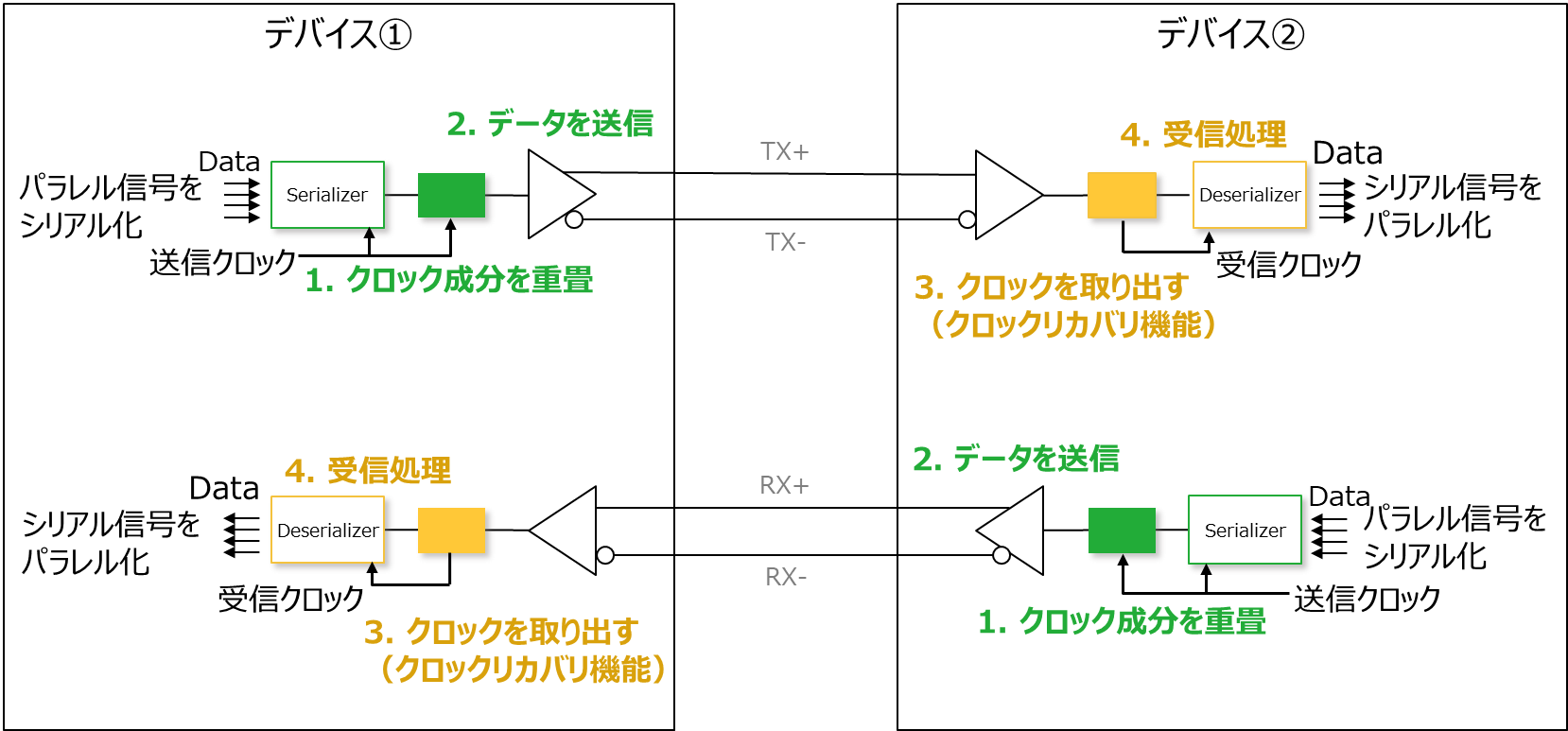

「送信クロック」と「受信クロック」は、以下の仕組みによって同期されます。

送信側:

- 送信処理に使用する「送信クロック」のクロック成分をデータに重畳

- データを送信

受信側:

- クロックリカバリ機能により、受信データからクロック成分を取り出す

- 取り出したクロックで位相合わせを行い、「受信クロック」を最適化

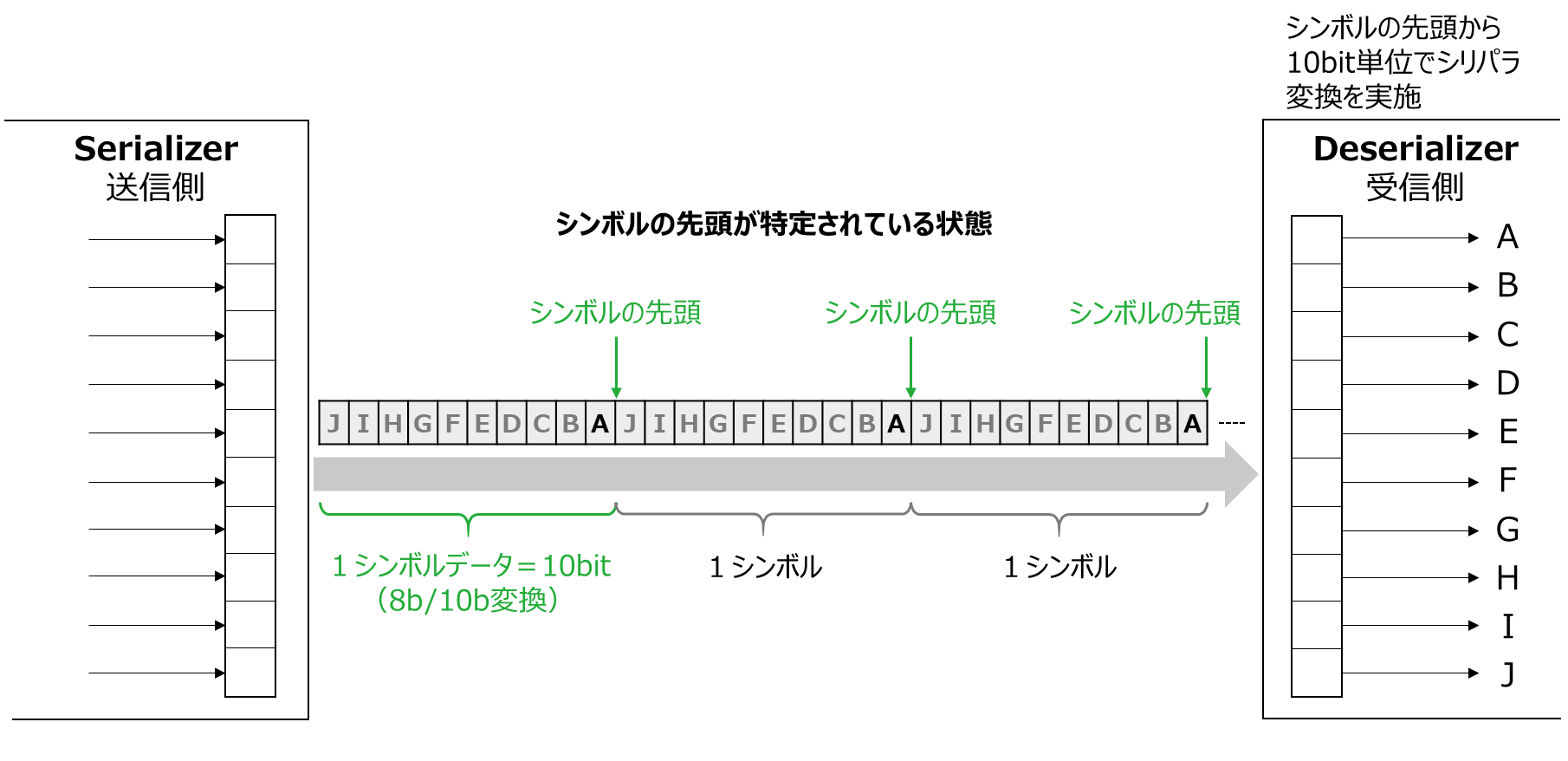

シンボル同期(Gen1, Gen2の場合)

デシリアライザが受信データのシンボル開始位置を特定し、シンボル毎にシリアルからパラレルデータへ変換できるようにすること。

一度シンボルの先頭位置が特定されると、その位置を起点とする10bitごとのシンボル単位でシリアル→パラレルデータ変換を行います。(1シンボルの8b/10b変換については、本連載の第1回を御参照ください。)

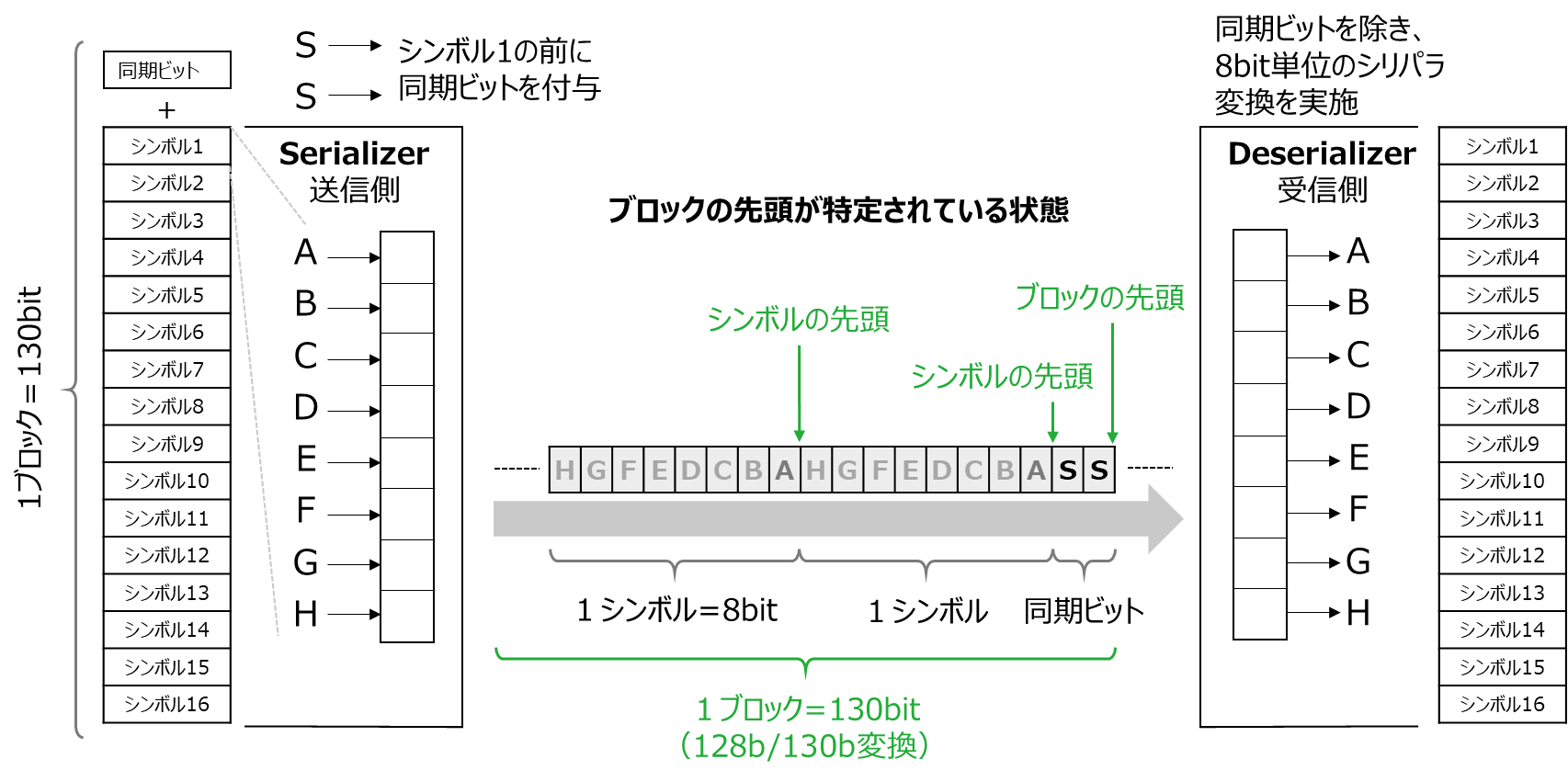

ブロック同期(Gen3以上の場合)

デシリアライザが受信データのブロック開始位置を特定し、ブロック毎にシリアルからパラレルデータへ変換すること。

Gen 3以上においては、前述のシンボル同期ではなくブロック同期を行い、受信データのブロック開始位置の特定を行います。ブロックの先頭に位置する同期ビット(2bit)を起点とし、130bitのブロックを受信します。

1ブロックは同期ビット(2bit)+16シンボル(8bit x 16 = 128bit)で構成され、受信側のデシリアライザは8bit単位でシリアル→パラレルデータ変換を行います。(1ブロックの128b/130b変換については、本連載の第1回を御参照ください。)

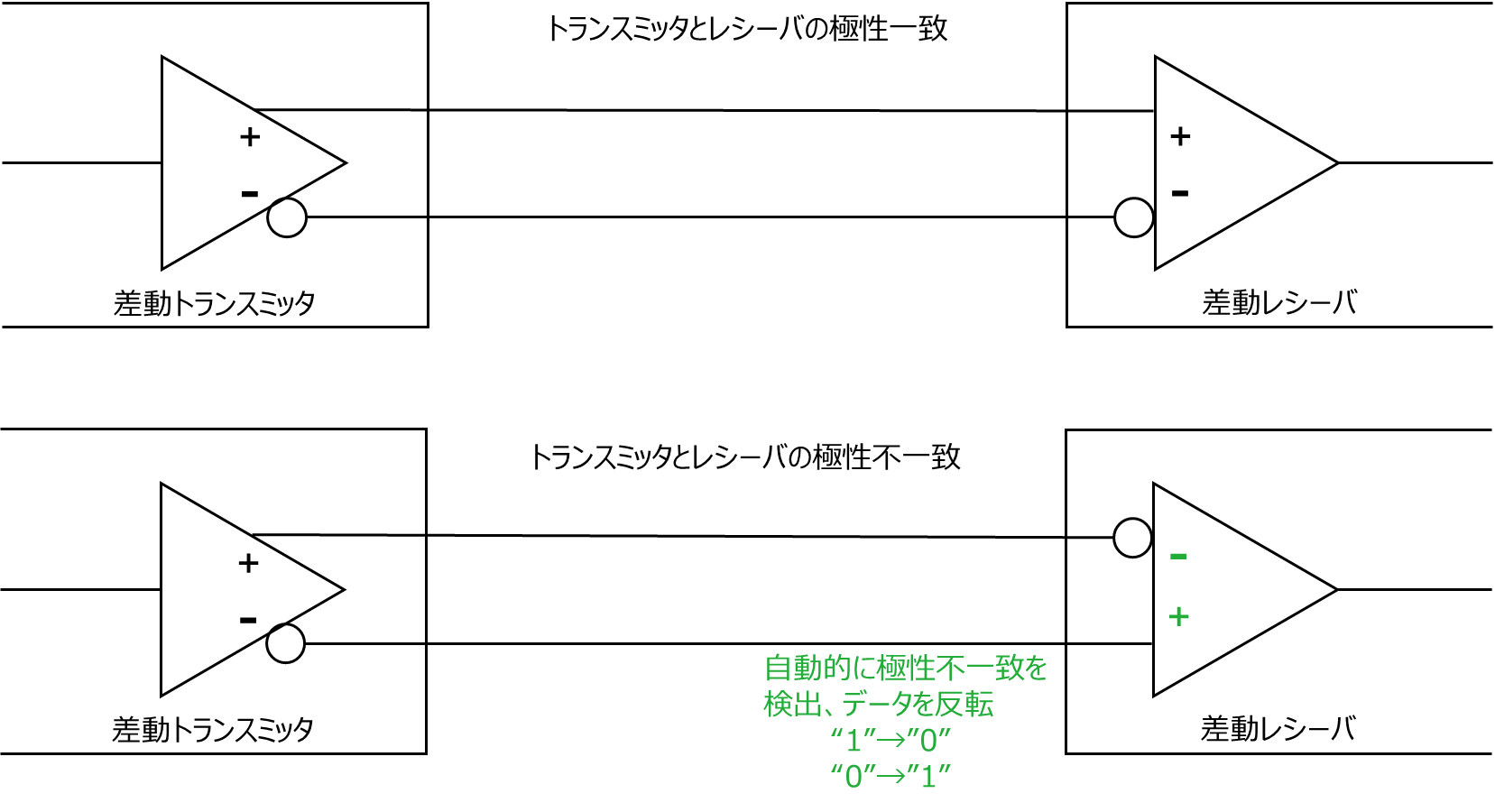

レーン極性調整

トレーニングデータ受信によりレーン極性(差動信号のD+とD-)の反転を検出し、受信データを反転すること。

差動トランスミッタと差動レシーバの極性が一致しない場合、差動レシーバ側で受信データの値を反転させます。(”1”→”0”, ”0”→”1”)

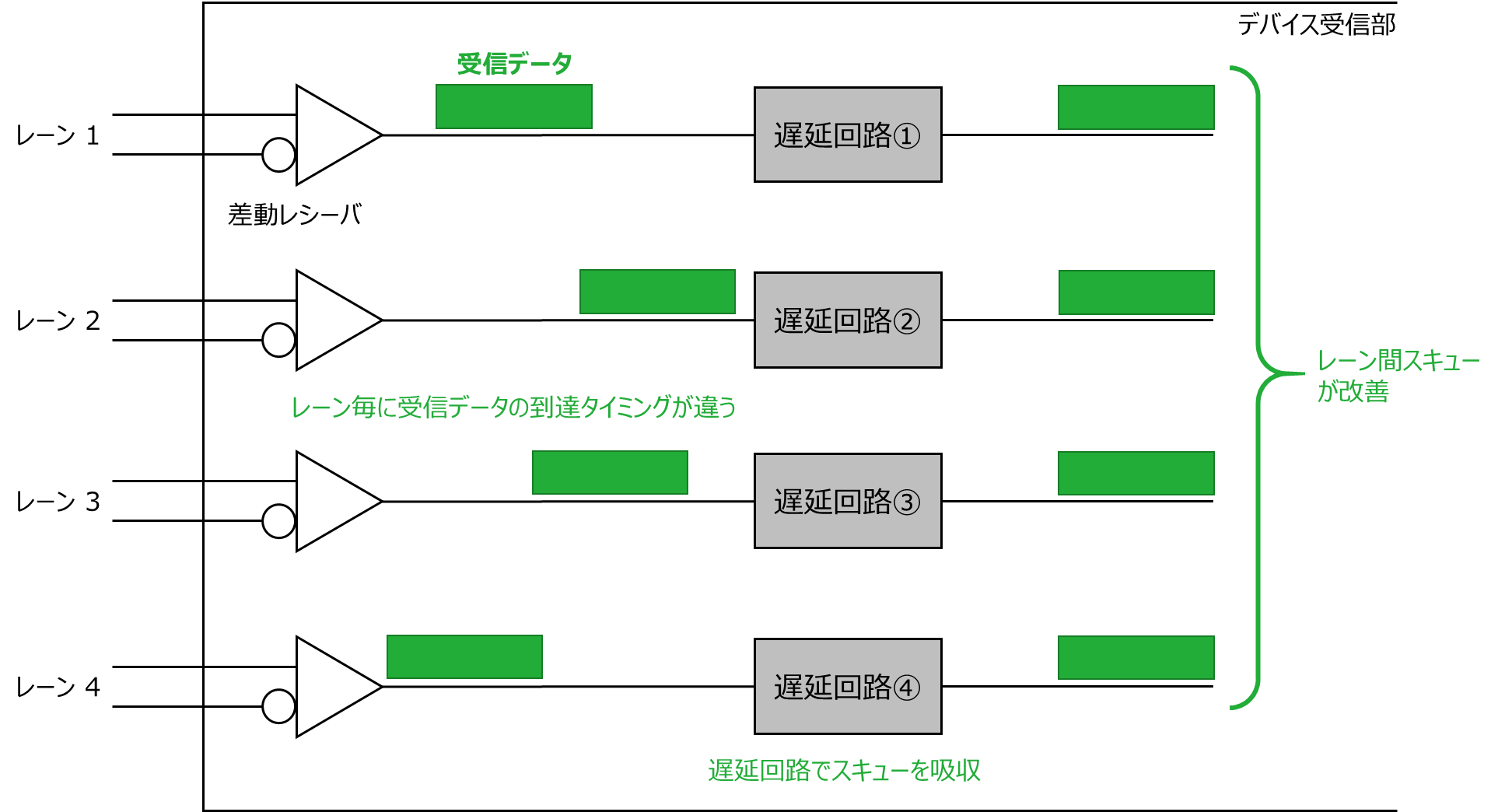

レーン間デスキュー

マルチ・レーン構成で、レーン間に発生するスキューを除去すること。

マルチ・レーン構成の場合、送信側デバイスの特性や伝送路長の違いによって、受信側に到達する信号のタイミングが一致しないことがあるため、各レーンごとに遅延回路を設け、タイミングの違いを吸収します。このようなレーン間の時間差を「レーン間スキュー」と呼び、そのスキューを除去することを「レーン間デスキュー」と呼びます。

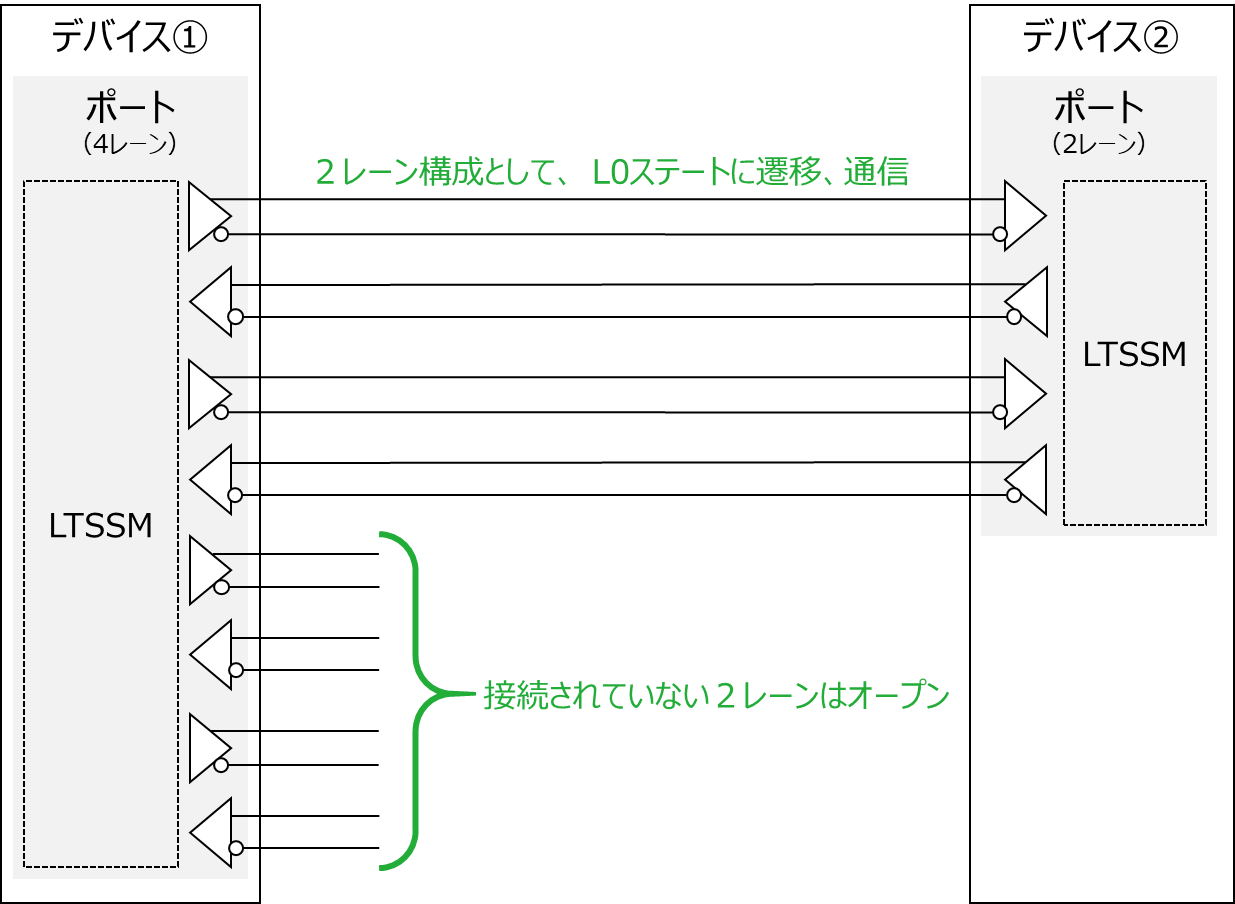

レーン構成の確立

PCI Expressのリンク幅を決定し、レーン構成を確立させる機能。

例えばデバイス➀のポートは4レーン構成ですが、そのうち2レーンのみがデバイス②と接続されている場合、これら接続されている2レーンのリンク幅で通信可能状態となります。PCI Express規格で規定されているリンク幅は、1, 2, 4, 8, 12, 16, 32, 64レーンの8種類です。

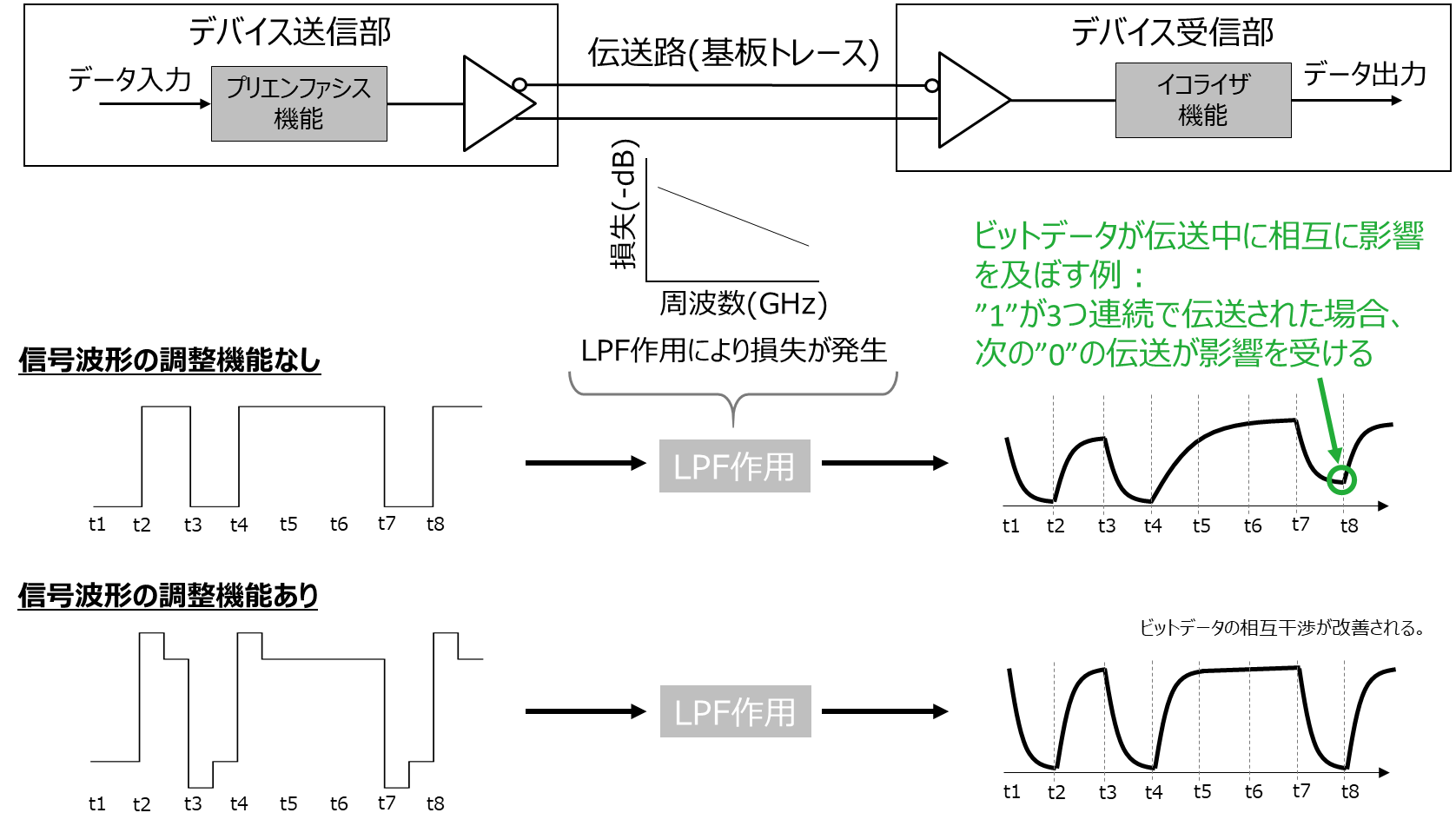

信号波形調整機能のチューニング

送信部のプリエンファシス機能、受信部のイコライザ機能の調整を行い、伝送波形品質を向上させること。

特性上、基板トレースはローパス・フィルタ(低域通過フィルタ)として作用する為、周波数の高い信号は減衰し、伝送距離が長くなるほど減衰量が増し、信号波形は大きく変形します。このためビットデータ間で相互に干渉が発生し、正確にデータを伝送することが難しくなります。

このビットデータの相互干渉問題を改善するため、 PCI Expressでは送信側・受信側それぞれに、信号波形の調整機能が採用されています。

送信側:プリエンファシス機能(伝送路上で減衰する高周波成分を送信前に増幅)

受信側:イコライザ機能(伝送路上で減衰した高周波成分を増幅)

4. まとめと次回の内容

第3回の今回は、PCI Expressの信頼性の高い接続について説明致しました。

PCI Expressでは、内蔵するLTSSMとトレーニング・シーケンスの実施により、ホスト、スイッチ、エンドポイント間におけるリンク状態を管理することに加え、送受信波形の調整を行うことで安定した高速通信を実現しています。これらの機能・性能を備えたPCI Expressは、高い信頼性を持つ接続方式である、と言えます。

次回の第4回は、PCI Expressの信頼性の高い転送方式について説明します。