LVDSの規格解説!設計時に気を付けるべきポイントとは?

........

- 更新日

- 2025.06.30

- 公開日

- 2024.11.29

高速通信ではディファレンシャル伝送が当たり前になり、その通信速度も日々高速化しています。今回は映像データの伝送、特に液晶モジュールの駆動で使用される高速通信規格 LVDSに関して、規格の概要から基板設計時の注意点を解説します。

※動画で概要を知りたい方はこちらから!

1. LVDSとは?規格の概要と対象アプリケーション

LVDSはLow Voltage Differential Signalingの略でデジタル信号を短距離で有線伝送するための技術です。小振幅・低消費電力で比較的高速の差動インタフェースで、液晶モジュールの映像入力インタフェースとしてよく使われます。

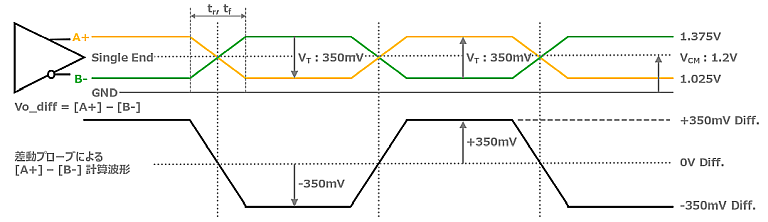

1995年に“ANSI/TIA/EIA-644”として標準化されたシリアルインタフェース向けの物理層仕様です。終端抵抗100Ω、中心電圧 1.2V、差動振幅 350mV、3.5mAの定電流源で駆動します。データ伝送速度は最大655Mbpsと定められています。

| 項目 | シンボル | 単位 | 最小値 | 平均値 | 最大値 |

|---|---|---|---|---|---|

| オフセット電圧 | VCM | V | 1.125 | 1.2 | 1.375 |

| 差動出力電圧 | VT | mV | 247 | 350 | 454 |

| オフセット電圧変動 | |VT|-|VT*| | |mV| | - | - | 50 |

| 短絡電流 | |ISA|, |ISB| | |mA| | - | - | 24 |

| 立ち上がり時間 | tr | ps | 260 | - | 0.3 tui |

| 立下がり時間 | tf | ps | 260 | - | 0.3 tui |

| 入力電流 | Iia, Iib | μA | - | - | 20 |

| 終端抵抗 | ZT | Ω | 90 | 100 | 132 |

| 差動入力電圧閾値 | - | |mV| | - | - | 100 |

| 差動入力電圧範囲 | |VID| | |mV| | 100 | - | 600 |

| 入力電圧範囲 | - | V | 0 | - | 2.4 |

-

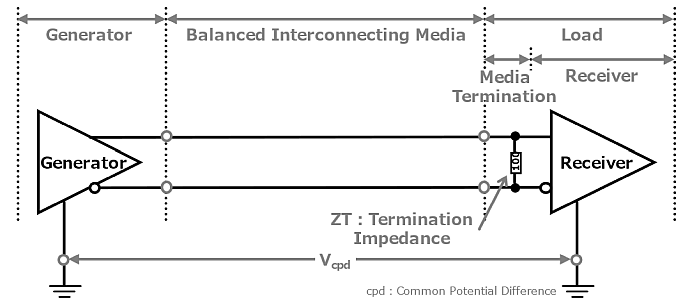

図1 LVDSインタフェース回路

-

図2 LVDSドライバ/レシーバ概略図

2本の差動信号(ポジティブ[A+]、ネガティブ[B-])を1.2Vのコモンモード電圧を中心に信号間を350mVの電位差でスイングさせることで信号を伝送します。この信号をオシロスコープの差動プローブで測定すると、シングルエンドのような信号波形が得られ、シングルエンドの信号と同じようにデータを確認することが可能です。

LVDSは主にWVGA(800×480)以上の解像度を持つ液晶モジュールの映像入力インタフェースとして利用されています。VGA(640×480)以下の解像度に関してはシングルエンドのRGBパラレルが利用されており、高解像度の液晶モジュールではeDP、モバイル向け液晶モジュールではMIPI-DSIなどアプリケーションに合わせてインタフェースがリリースされています。

その他に、シングルエンドのパラレル信号をLVDSに変換するSerDES(シリアライザ・デシリアライザ)も提供されており、液晶モジュール以外での信号伝送も可能となっています。

2. 差動信号とシングルエンド信号

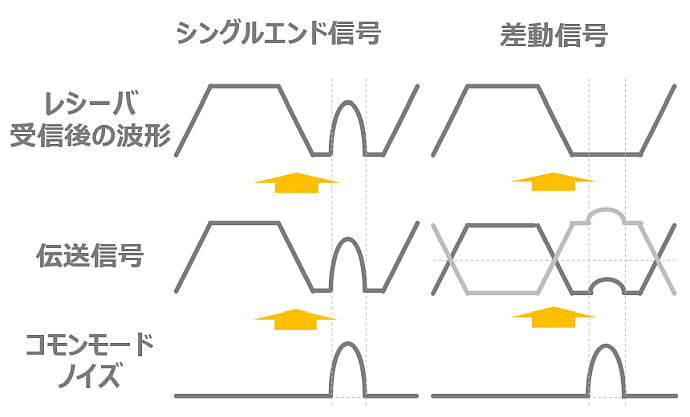

シリアル通信記事で簡単に説明しましたが、シングルエンド(不平衡)と差動(ディファレンシャル/平衡)の違いは一つの信号を1本の信号線で伝送するか、2本の信号線で伝送することです。

シングルエンドは信号線が1本のため、単純に基板/ハーネスの配線数・パッケージ/コネクタの端子数が最低限となるのでコスト的に優位ですが、ノイズの影響を受けやすくなるため配線の取り回しには注意が必要です。シングルエンドは、UART、SPI、I2C、I2Sなどマイコンで良く使われる比較的低速な通信で用いられます。

-

マイコンに使われるシリアル通信に関しては、こちらをご参照ください。

-

【マイコン講座】シリアル通信 はじめの一歩と"落とし穴"

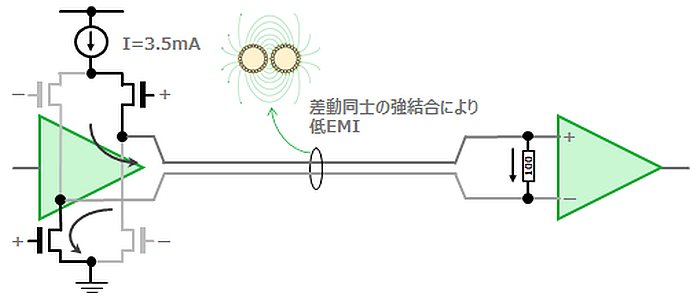

LVDSで用いられる差動は信号線が2本となるため、単純にシングルエンドの倍の配線・端子が必要となるのでコスト的には厳しくなりますが、コモンモードノイズの影響を受けにくくなります。また、基準電圧をベースに対称な信号を発生させるため放射ノイズも抑えることが可能です。LVDSは特に基準電圧の低電圧化を図っており、駆動に必要な電流も少ないため、放射ノイズは低くなります。

差動はRS422/485、Sub-LVDS、MIPI D-PHY、DisplayPort、DVI(T.M.D.S.)、Ethernet、PCIeなど低速~高速まで多くの規格で利用されています。低速のものは長距離伝送/ノイズ耐性を目的として、高速のものは映像データのような高速/大容量を目的として採用されています。

| LVDS | eDP | MIPI D-PHY | DVI(T.M.D.S.) | |

|---|---|---|---|---|

| 信号線1ペア当たりのデータ伝送速度 | 655Mbps | 2.7Gbps/1.62Gbps | 1.5Gbps | 550Mbps |

| ペア数(レーン数) | 3 or 4 | 2 | 4 | 3 |

| 専用クロック | あり | なし | なし | あり |

| 符号化方式 | なし | 8B/10B | 8B/10B | 8B/10B |

| 結合方式 | DC結合 | AC結合 | AC結合 | AC結合 |

| 規格団体 | ANSI/TIA/EIA | VESA | MIPI Alliance | DDWG |

3. LVDSとRGBの違い

先述した通り、RGBは主に低解像度の液晶モジュールで利用されており、WVGA以上の解像度ではLVDSが主流となっています。液晶コントローラ内蔵マイコンでは主にRGBが搭載されており、一部のマイコンでMIPI D-PHYもサポートされています。SoC/プロセッサでは高解像度の映像信号をサポートするためRGB、LVDS、MIPI D-PHYなど複数規格を搭載したものがリリースされています。

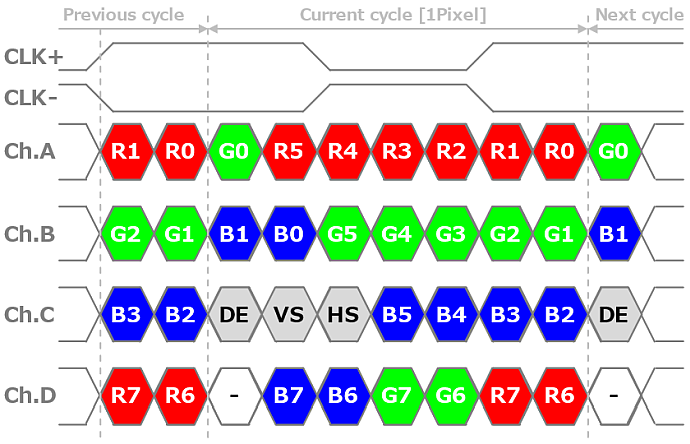

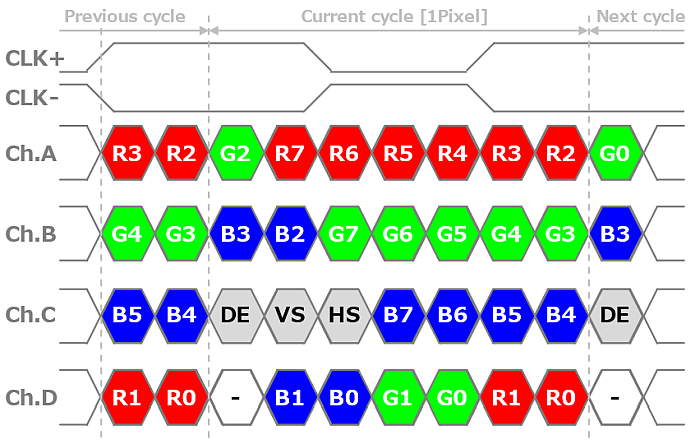

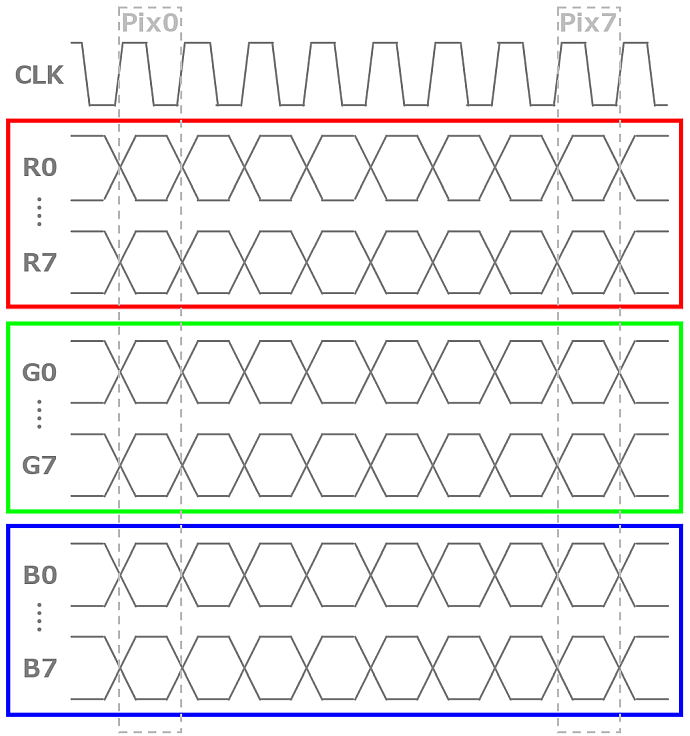

RGBでは各色/ビットごとに信号線があり、RGB666ではクロックと合わせて19本、RGB888では同25本の信号線が用いられます。LVDSでは3channel/4channel、Single Link/Dual Linkがあり、3channel・Single Link 6本から4channel・Dual Link 16本まで幅があります。RGBではパラレル伝送で多くの信号線を必要としましたが、LVDSではシリアル伝送となるため伝送量の大容量化(高解像度化)と信号線の削減を両立しています。

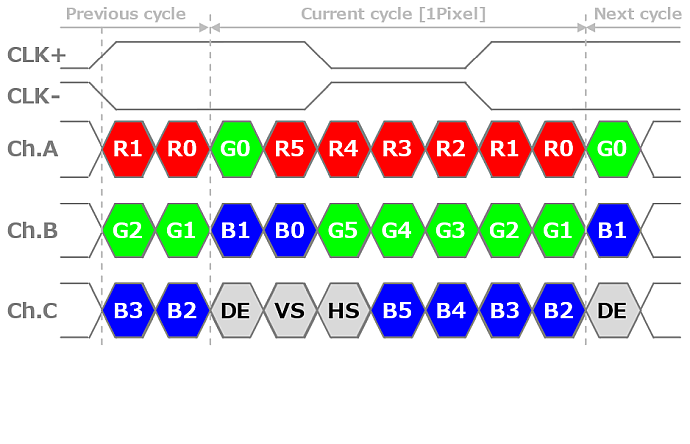

LVDSではシリアル化する際に信号フォーマットとしてVESAとJEITAの2種類のフォーマットがあるため、どのフォーマットで伝送するのか液晶モジュール側の仕様に注意する必要があります。

-

図6 18bpp, VESA/JEITA伝送フォーマット(クリックで拡大表示します)

-

図7 24bpp, VESA伝送フォーマット(クリックで拡大表示します)

-

図8 24bpp, JEITA伝送フォーマット(クリックで拡大表示します)

4. LVDS/差動信号の設計ポイント

LVDS/差動信号を用いることで高速伝送・ノイズ耐性強化が図れますが、基板設計の際には特有の注意が必要です。本項では液晶モジュールへの映像配線をベースとして、基本的な基板設計時のポイントを整理します。

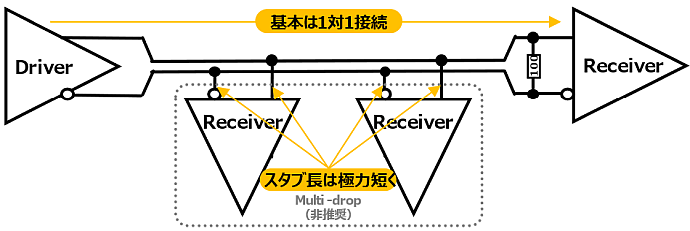

1. ドライバとレシーバを1対1で接続

- マルチドロップは推奨されません

- マルチドロップが必要な場合、スタブ長は最短(20mm未満)としましょう

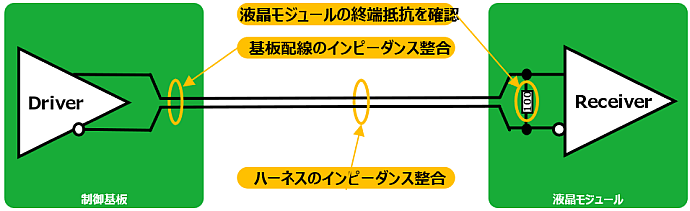

2. 終端抵抗とインピーダンスマッチ

- 液晶モジュールではモジュール内に終端抵抗が配置されていることが一般的です

液晶モジュール内に終端抵抗が内蔵されていることを確認しましょう - 終端抵抗の抵抗値(90~130Ω)に合わせて配線のインピーダンスマッチを指定しましょう

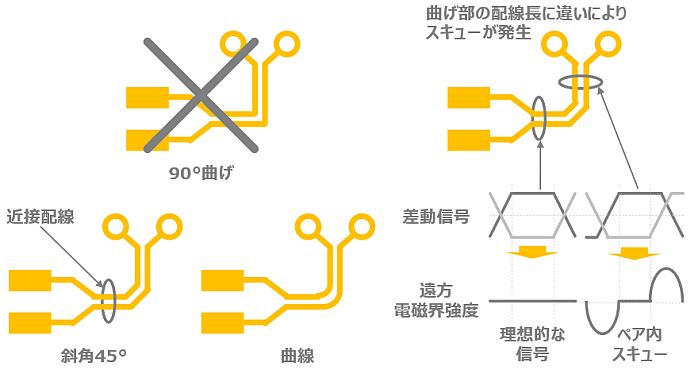

3. PCB上での配線

- 配線を曲げる際は45°もしくは斜角を設けましょう

-

差動ペアは可能な限り近接させてルーティングしましょう

近接させることで磁界を打ち消す働きが強くなります - 差動ペアの導体間信号スキューを最小限に抑えましょう

ペアの一方の信号が他方より速くレシーバに到達すると、信号ペア間に位相差が発生してコモンモードノイズの要因となります

配線の曲げにより配線長に差が生じますので、等長となるように注意しましょう

4. 基板構成、リターンパス

- インピーダンス管理には均一なグランド層が有効です

4層以上のPCBを使用し、内層に電源・グランド層を配置しましょう - LVDS 信号の下に設けた一様で切れ目のないグラウンド層が最良の電流リターン・パスになります

グランド・リターン・パスを設けましょう - ノイズの多いシングルエンドCMOS/TTL信号はクロストークを与える可能性があります

CMOS/TTL信号はLVDS信号から離して配線しましょう

-

基板上のノイズ対策に関しては、こちらの記事の合わせてお読みください。

-

避けては通れない「EMI対策」

5. まとめ

-

LVDSの規格から用途、基本的な設計ポイントまでを記載しましたが如何でしたでしょうか?基板設計に関しては、まだまだ気を付けなければならないポイントが御座いますが、それらに関しては別記事やアートワーク設計ウェビナなどもご参考にしてください。

その他にも液晶/GUI関係の記事を掲載しておりますので、合わせてお読みいただければ幸いです。

-

アートワーク設計ウェビナ

(執筆:木庭マサヒロ)